Xilinx released the first details of its next-generation Everest architecture, now called Versal. It shows the microprocessor landscape is blurring as CPUs, GPUs and FPGAs morph into increasingly similar SoC-like devices.

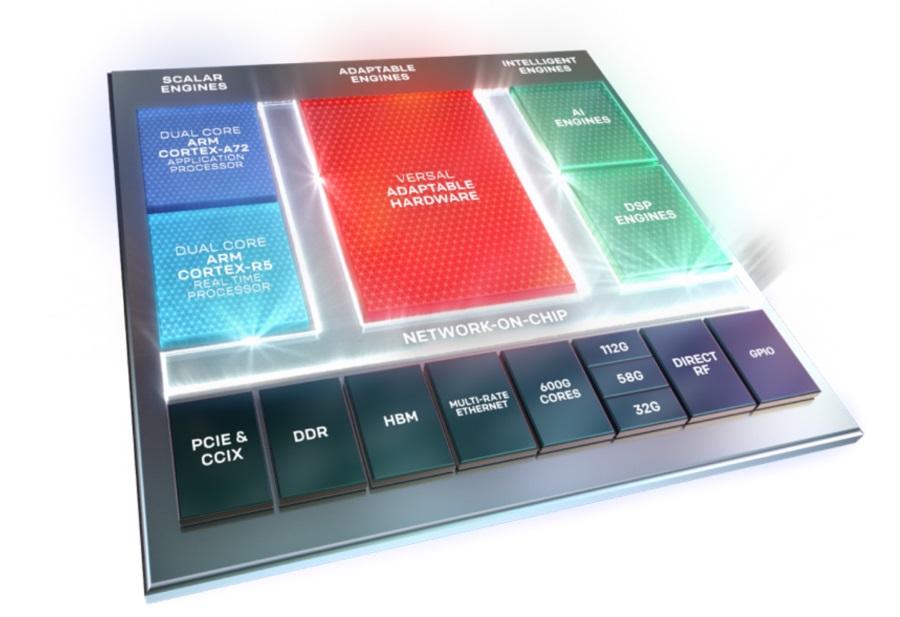

Versal shrinks the size of a central FPGA block to make room for more ARM, DSP, inference and I/O blocks. It comes as Intel and AMD make room for beefier GPUs in their x86 chips and Nvidia adds specialty cores for jobs like deep learning on its GPUs.

Xilinx positioned Versal as the start of a broad new family of standard products. They aim to outperform CPUs and GPUs on a wide range of data center, telecom, automotive and edge applications and increasingly support programming in high-level languages such as C and Python.

At a time when Moore’s law is slowing, Versal is Xilinx’s effort to “step up its game to be a peer of Intel and Nvidia,” giants three to 20+ times its size, said analyst Kevin Krewell of Tirias Research.

Under the covers, Versal sports a network-on-chip (NoC) based on hardened AXI blocks and a management controller aimed to deliver new levels of programmability and ease of use. It also supports a new homegrown inference accelerator.

Xilinx released a handful of benchmarks based on simulations showing initial 7nm chips can beat 16-12nm CPUs and GPUs. First chips will tape out later this year, and initial Versal products will arrive in the second half of 2019.

Like the silicon, the software is still a work in progress. The company will announce Tuesday new C-language capabilities for Versal and its existing 16nm FPGAs on data center applications. A unified software environment for high-level languages is about a year away.